# Brick and Mortar Chip Fabrication

Martha Allen Kim

A dissertation submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

University of Washington

2008

Program Authorized to Offer Degree: Computer Science and Engineering

## University of Washington Graduate School

This is to certify that I have examined this copy of a doctoral dissertation by

## Martha Allen Kim

and have found that it is complete and satisfactory in all respects, and that any and all revisions required by the final examining committee have been made.

| Chair of t | he Supervisory Committee: |

|------------|---------------------------|

|            |                           |

|            | Mark Oskin                |

|            |                           |

| Reading (  | Committee:                |

|            |                           |

|            | Mark Oskin                |

|            | Susan Eggers              |

|            | Todd Austin               |

|            |                           |

| Date:      |                           |

In presenting this dissertation in partial fulfillment of the requirements for the doctoral degree at the University of Washington, I agree that the Library shall make its copies freely available for inspection. I further agree that extensive copying of this dissertation is allowable only for scholarly purposes, consistent with "fair use" as prescribed in the U.S. Copyright Law. Requests for copying or reproduction of this dissertation may be referred to Proquest Information and Learning, 300 North Zeeb Road, Ann Arbor, MI 48106-1346, 1-800-521-0600, to whom the author has granted "the right to reproduce and sell (a) copies of the manuscript in microform and/or (b) printed copies of the manuscript made from microform."

| Signature |  |  |

|-----------|--|--|

|           |  |  |

|           |  |  |

| Date      |  |  |

### University of Washington

## Abstract

Brick and Mortar Chip Fabrication

Martha Allen Kim

Chair of the Supervisory Committee:

Professor Mark Oskin

Computer Science and Engineering

While Moore's Law has advanced the semiconductor and technology industries, it has simultaneously driven up the cost of engineering a chip in a modern silicon process. The result is that fewer and fewer chips are produced in larger and larger volumes, stifling hardware diversity.

This thesis introduces *brick and mortar* chips, which aim to obtain the benefits of Moore's Law without the financial side effects. Brick and mortar chips are made from small, pre-fabricated hardware components (called bricks) that are bonded in a designer-specified arrangement to a communication backbone chip which serves as the mortar (called the I/O cap).

Our research examines several aspects of this chip manufacturing system. We develop a family of functional bricks, demonstrating a methodology for developing families that make efficient use of physical computation and communication resources. For high-performance communication between arbitrary combinations of bricks we propose a polymorphic onchip network. This network allows a single I/O cap to be configured to implement the ideal network for any particular application. We analyze a low-cost, physical component assembly technique called fluidic self-assembly, and find that the chip production rate is intertwined with the architectural design of the components. To minimize application execution time on these partitioned chips, we develop software partitioning and mapping techniques which balance communication costs against computational resource contention.

We close with a case study: an analysis of a brick and mortar implementation of a chip multiprocessor. Despite this being a highly latency sensitive design, our measurements indicate a worst case 36% average slowdown in application execution compared to a traditional, monolithic chip. Based on this, our cost analysis, and a survey of related technologies, we conclude that brick and mortar offers the best available performance for its price.

# TABLE OF CONTENTS

|           |                                                     | Page  |

|-----------|-----------------------------------------------------|-------|

| List of 1 | Figures                                             | . iii |

| List of   | Tables                                              | . v   |

| Chapter   | r 1: Introduction                                   | . 1   |

| 1.1       | The problem with Moore's Law                        | . 1   |

| 1.2       | Brick and mortar overview                           | . 2   |

| 1.3       | Contributions of the thesis                         | . 6   |

| 1.4       | Thesis outline                                      | . 7   |

| Chapter   | r 2: Manipulating the Economics of Chip Fabrication | . 8   |

| 2.1       | ASIC cost model                                     | . 8   |

| 2.2       | Opportunity for brick and mortar                    | . 9   |

| 2.3       | Brick and mortar cost model                         | . 12  |

| 2.4       | Quantifying the advantage of brick and mortar       | . 12  |

| Chapter   | r 3: Polymorphic On-Chip Network                    | . 15  |

| 3.1       | On-chip network design space exploration            | . 15  |

| 3.2       | Polymorphic network microarchitecture               | . 20  |

| 3.3       | Example configurations                              | . 24  |

| 3.4       | Polymorphic fabric parametrization                  | . 26  |

| 3.5       | Evaluation of fabric flexibility                    | . 30  |

| Chapter   | r 4: Empirical Brick Family Design                  | . 33  |

| 4.1       | Brick form factor                                   | . 33  |

| 4.2       | Function selection                                  | . 34  |

| 4.3       | Technology selection                                | . 35  |

| 1.1       | Rrick assignments                                   | 36    |

| Chapter  | 5: Hardware Component Assembly and Packaging                        |

|----------|---------------------------------------------------------------------|

| 5.1      | Fluidic self-assembly                                               |

| 5.2      | Interaction with architecture                                       |

| 5.3      | Component binning                                                   |

| 5.4      | External communication                                              |

| Chapter  | 6: Spatial Application Scheduling                                   |

| 6.1      | Tiled architectures                                                 |

| 6.2      | Overview of WaveScalar                                              |

| 6.3      | Hierarchical approach to scheduling                                 |

| 6.4      | Experimental evaluation                                             |

| 6.5      | Fine-DAWG scheduler                                                 |

| 6.6      | Fine-DAWG evaluation                                                |

| Chapter  | 7: Experimental Evaluation of Made-to-Order Chip Multiprocessors 68 |

| 7.1      | Methodology                                                         |

| 7.2      | Performance results                                                 |

| 7.3      | Exploiting process variation                                        |

| Chapter  | 8: Related Technologies                                             |

| 8.1      | Custom circuit implementation                                       |

| 8.2      | Chip carriers and the I/O cap                                       |

| 8.3      | On-chip communication networks and the polymorphic fabric           |

| 8.4      | Multi-die assemblies                                                |

| 8.5      | Self-assembly techniques                                            |

| 8.6      | Spatial application scheduling                                      |

| Chapter  | 9: Variations, Future Research, and Conclusions                     |

| 9.1      | Variations on brick and mortar                                      |

| 9.2      | Future research                                                     |

| 9.3      | Conclusion                                                          |

| Bibliogr | aphy                                                                |

# LIST OF FIGURES

| Figure 1 | Number                                                                                                                               | Рε | age |

|----------|--------------------------------------------------------------------------------------------------------------------------------------|----|-----|

| 1.1      | Cross-section of brick and mortar chip                                                                                               |    | 3   |

| 2.1      | Effect of increased non-recurring engineering costs on chip production cost at different market sizes and price points               |    | 11  |

| 2.2      | Comparison of total production cost for ASIC and brick and mortar chips as a function of batch size                                  |    | 12  |

| 2.3      | Brick and mortar threshold batch size as a function of brick and I/O cap production volume                                           |    | 13  |

| 3.1      | Latency and throughput of on-chip interconnect design space                                                                          |    | 19  |

| 3.2      | Microarchitecture of the polymorphic on-chip network                                                                                 |    | 22  |

| 3.3      | Instantiation of a fat tree network in polymorphic fabric. The links that form the mesh connections between root nodes are not shown |    | 25  |

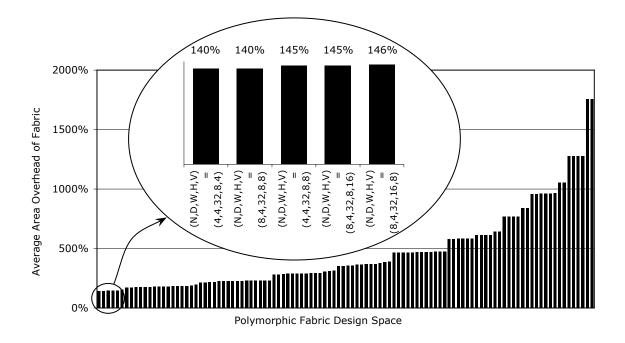

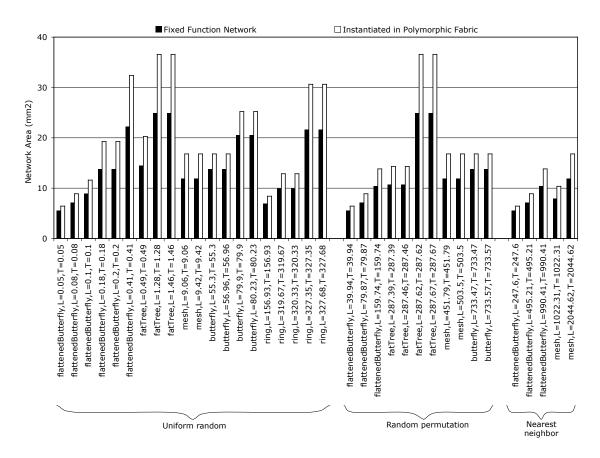

| 3.4      | Average area overhead of each polymorphic fabric across instantiations of all members of the on-chip network design space            |    | 29  |

| 3.5      | Area overhead of most efficient polymorphic fabric when configured with                                                              |    |     |

|          | Pareto optimal networks.                                                                                                             |    | 31  |

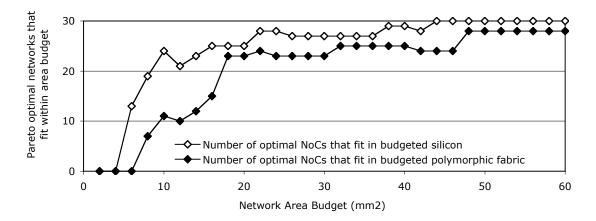

| 3.6      | Flexibility of polymorphic fabric as a function of the network area budget                                                           | •  | 31  |

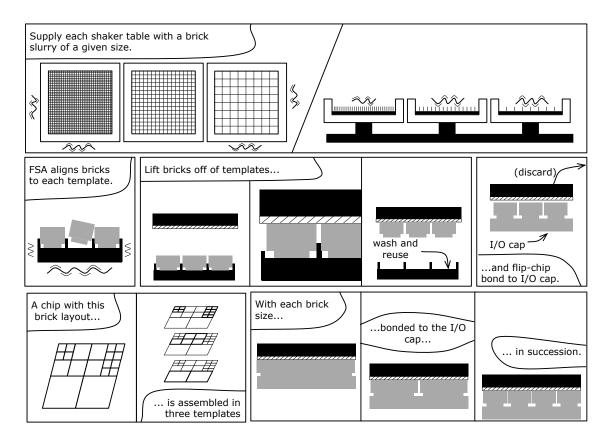

| 5.1      | Fluidic self-assembly of a brick and mortar chip                                                                                     |    | 40  |

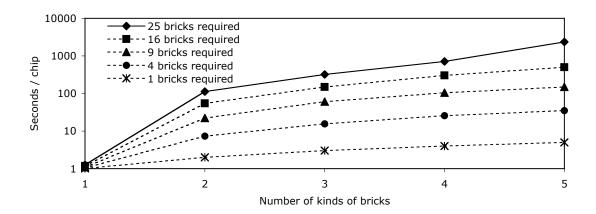

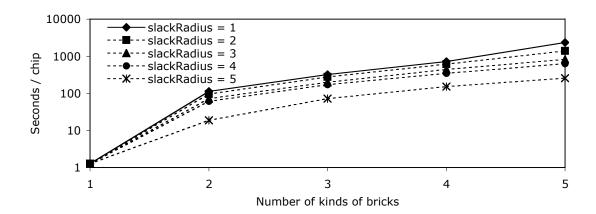

| 5.2      | Brick and mortar chip assembly time as a function of brick heterogeneity and design size                                             |    | 43  |

| 5.3      | Brick and mortar chip assembly time as a function of brick heterogeneity and brick placement relaxation                              |    | 44  |

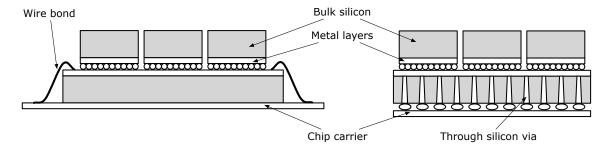

| 5.4      | Two alternatives for brick-and-mortar-chip-to-carrier communication: wire bonds and through silicon vias                             |    | 46  |

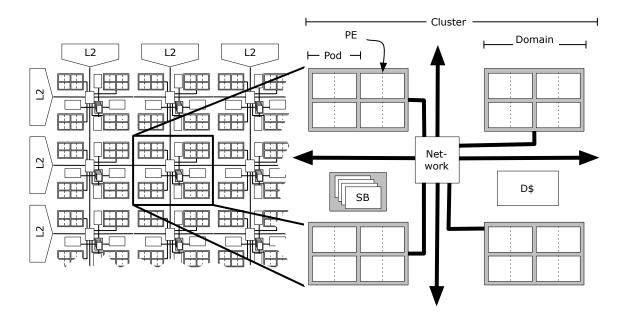

| 6.1      | Microarchitecture of the WaveScalar processor                                                                                        |    | 51  |

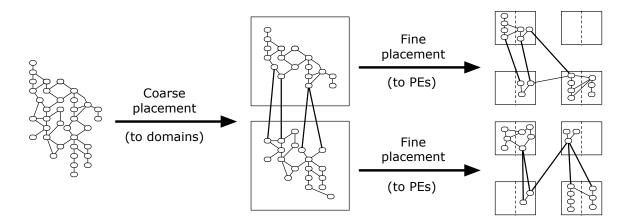

| 6.2      | Coarse and fine stages of hierarchical instruction placement on WaveScalar.                                                          |    | 53  |

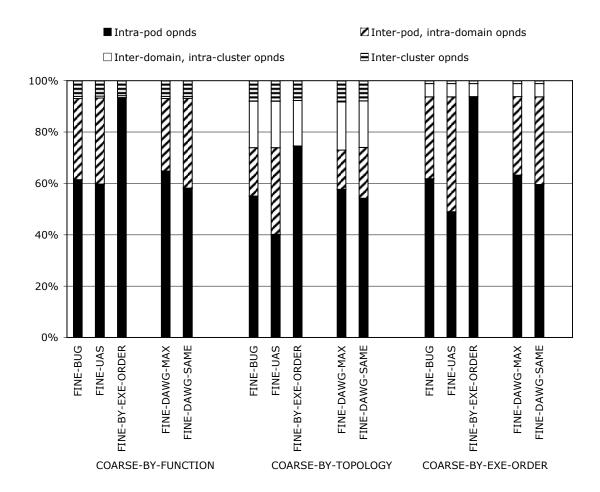

| 6.3      | WaveScalar operand traffic breakdown by instruction scheduler                                                                        |    | 58  |

| 6.4      | WaveScalar ALU conflicts by instruction scheduler                                                                                    |    | 59  |

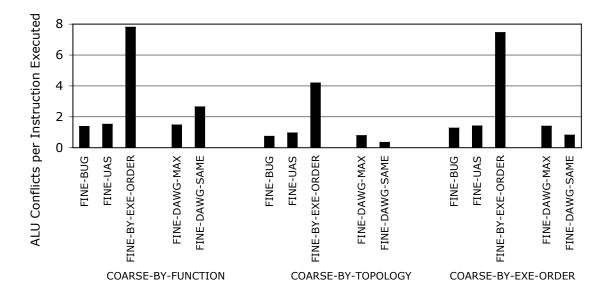

| 6.5      | Communication latency and resource conflict trade-off achieved by FINE-DAWG                                                          |    | 64  |

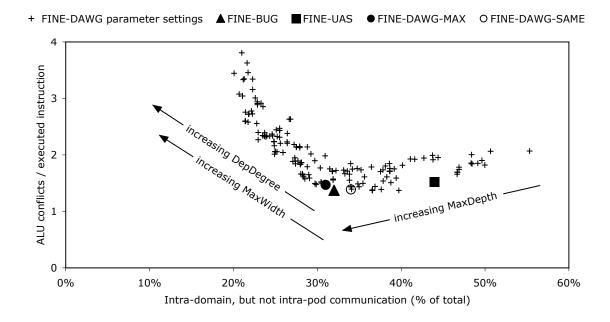

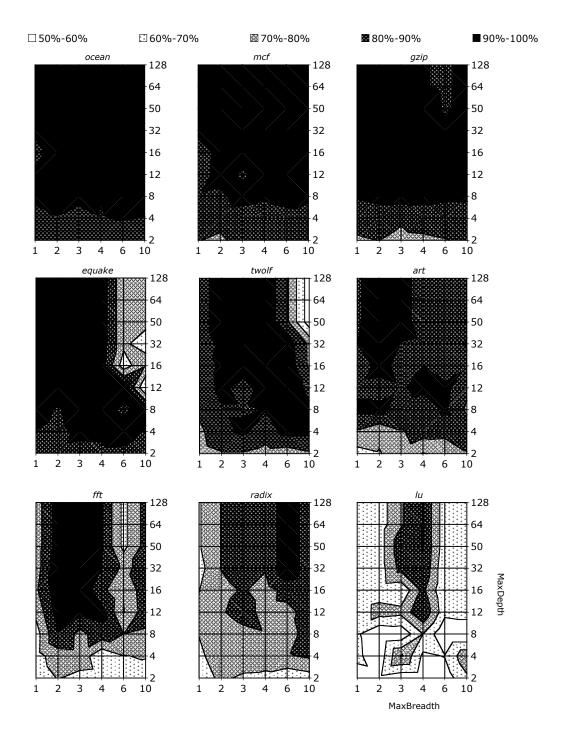

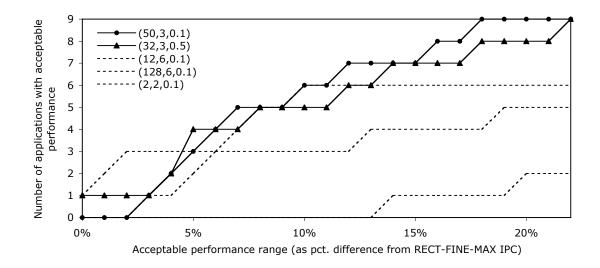

| 6.6 | Application performance sensitivity to FINE-DAWG parameters                                                                                          | 65 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 6.7 | Cumulative distribution function of selected Fine-DAWG parameters: the best two parameter settings (solid lines) and three representing the range of |    |

|     | 160 others (dashed lines)                                                                                                                            | 67 |

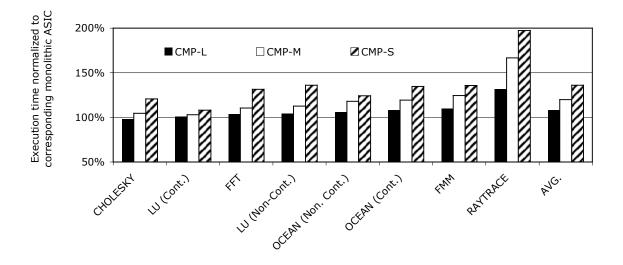

| 7.1 | Application runtime on brick and mortar CMP compared to a monolithic ASIC CMP                                                                        | 71 |

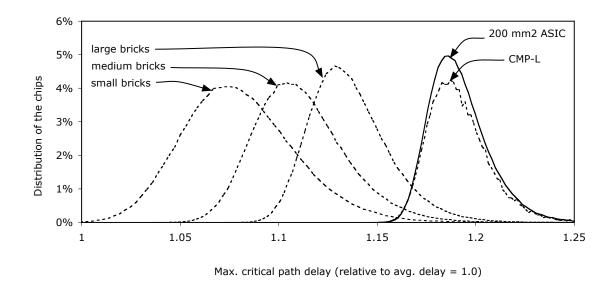

| 7.2 | CMP and component clock speed variation derived from FMAX models                                                                                     | 72 |

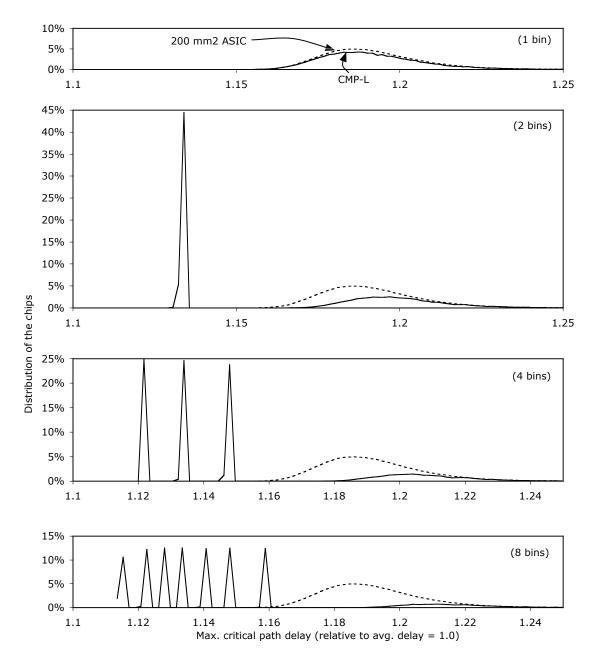

| 7.3 | Effects on chip speed of pre-assembly component speed binning                                                                                        | 74 |

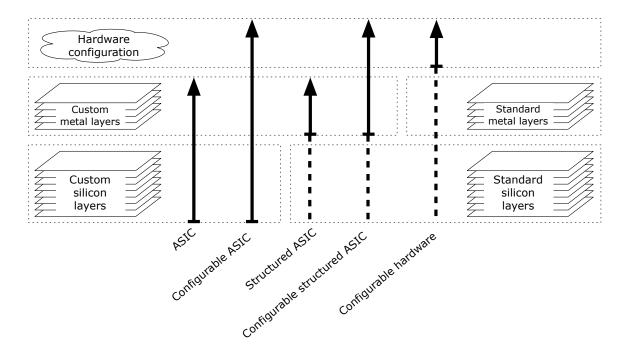

| 8.1 | Classification of circuit implementation technologies                                                                                                | 78 |

# LIST OF TABLES

| Table Number Pa                                                                                                                                                             | $ag\epsilon$ |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 2.1 ASIC and brick and mortar chip cost models                                                                                                                              | 10           |

| <ul><li>3.1 On-chip network design space and hybrid synthesis-analytical area model</li><li>3.2 Polymorphic fabric design space and area and configuration models</li></ul> |              |

| 4.1 IP block synthesis results and brick assignments                                                                                                                        | 37           |

| 6.1 Micro-architectural parameters of the WaveScalar processor                                                                                                              |              |

| 7.1 Comparison of brick and mortar and monolithic implementations of three CMP designs                                                                                      | 69           |

### ACKNOWLEDGMENTS

I am very grateful for the support of Mark Oksin throughout my graduate career. Mark has been a reliable source of technical and professional guidance, with an astounding ability to cut to the quick of any issue. His advocacy, friendship, and easy manner – which guarantees me a laugh over my successes and failures alike – have been invaluable. Thank you also to Susan Eggers, who has provided mountains of thoughtful advice and feedback over the years, as an advisor, instructor, and mentor. Finally, many thanks to the other members of my committee, Todd Austin and John Sahr. They have graciously shared their time and thoughts with me and I am much obliged.

I have been fortunate to have a number of outstanding collaborators. John Davis has been at the ready as a sounding board, reader, and friend for some time now. In one short year Luis Ceze has discussed countless ideas with me, revitalizing the stagnant ones and refining the nascent ones. I was fortunate enough to join the architecture group soon after my arrival in graduate school. For many years now I have learned from and enjoyed the company of Steve Swanson, Andy Schwerin, Andrew Petersen, Andrew Putnam, and Lucas Kreger-Stickles. Thank you also, to Mojtaba Mehrara, for his perserverence in collecting the simulation and process variation data presented in this thesis.

I would like to thank the faculty and administrators that have made UW CSE such a congenial and supportive community for me. In particular, Hank Levy, Dan Grossman, Larry Snyder, David Notkin, Carl Ebeling and Ed Lazowska have been generous with their guidance and encouragement. Thank you also to Lindsay Michimoto for straightening the maze of university administrative policies before me.

I am unspeakably thankful for the support of my family. My parents have provided a steady stream of love and insight which has sustained me. My brother, Chris, is a model of determination. While I know I can never keep up with you, I would be happy to be the f who icis. Finally, thank you to my husband, Bryan, for many years of steadfast friendship. You are both cause and reward for all of those cross-country flights.

## Chapter 1

## INTRODUCTION

Technology scaling has produced a wealth of transistor resources and corresponding improvements in chip performance. However, these benefits come with an increasing price tag, due to rising design, engineering, and validation costs of modern chips [15]. The result has been a steady decline in unique application-specific integrated circuit (ASIC) designs that enter production [21]. This initiates a vicious cycle. Fewer unique chips means that fabs have fewer customers across which to amortize their costs, leading to even higher costs for those who do manufacture chips. The cycle completes as higher chip manufacturing costs exclude even more potential manufacturing customers.

## 1.1 The problem with Moore's Law

While Moore's Law has fueled the semiconductor industry, it has also fueled this spiral of increasing costs and shrinking fab customer bases. As transistors have shrunk, the cost of fabricating a semiconductor device has grown commensurately. While the fabrication cost per transistor has steadily declined [62], multiple other expenses have ballooned, contributing collectively to the growing total. For example, small features are more susceptible to process variation than larger ones, increasing the range of variation and the proportion of faulty chips. In addition, the smaller the transistor, the more of them that can fit in a given amount of silicon. The result is that circuit complexity has been increasingly outstripping designer productivity, in a phenomenon referred to as Moore's Law's corollary of "compound complexity" [143].

The industry has dealt with these challenges by increasing the engineering effort that goes into each chip. This effort manifests itself as larger design teams, or longer product cycles, and often both at once. The vast majority of this engineering effort is incurred once per chip design, and does not vary with the number of chips produced. Accordingly, this

expense is called the non-recurring engineering cost (NRE) of a chip. Industry analysts estimate that the NREs for a typical 90nm standard cell ASIC can range from \$5M up to \$50M [113].

Maintaining a particular price per chip in the face of skyrocketing NREs requires larger and larger batches of chips. This is because the single NRE is shared evenly across the population of chips produced. The larger the population, the smaller the impact of the NRE on individual chip cost, so chips produced in large batches cost less than chips produced in small batches. Growing NREs are pushing the line that divides "small" from "large" higher and higher. The result of this situation is that only high-volume chip manufacturers, or those who can sell smaller batches at high prices, can afford to be in the chip business.

Moreover, at the same time that complexity and engineering effort have been soaring, the commercial market has been demanding and rewarding short chip design cycles. This is due to shrinking product lifetimes and the increasing competitive importance of being the first to market with a new product. A technology that succeeds in reducing engineering effort will simultaneously attack the cost of chip preparation as well as its time to market. This research seeks to develop such a technology: one that reaps the benefits of Moore's Law (e.g., high clock speeds, integration) without incurring the downsides (e.g., high NRE costs, long time to market). A viable technology with these characteristics would serve markets that today are economically unreachable.

## 1.2 Brick and mortar overview

We propose a system, called *brick and mortar*, which is designed to allow fabricated ASICs to be used in many different chip designs. In this way, brick and mortar achieves high volume usage of the *individual* ASIC components while producing *small* batches of any given chip. The purpose is to reduce the non-recurring engineering costs as much as possible while maintaining, to the largest extent possible, the other benefits of ASICs.

### 1.2.1 Description

At the heart of the brick and mortar manufacturing technique are two architectural components: *bricks*, which are mass-produced pieces of silicon containing processor cores, memory

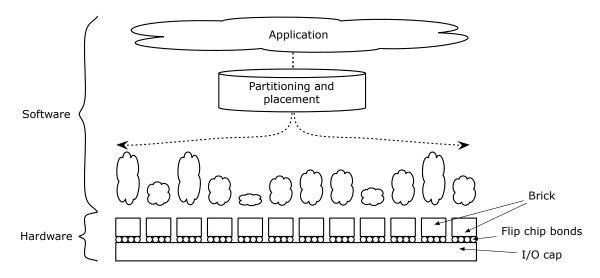

arrays, small gate arrays, DSPs, FFT engines, and other IP (intellectual property) blocks; and mortar, an I/O cap, that is a mass-produced silicon substrate containing inter-brick communication infrastructure and I/O support. In the brick and mortar process, engineers design chips by assembling an application-specific layout of bricks. This arrangement of bricks is then bonded, as illustrated in Figure 1.1, to the I/O cap that interconnects them.

Applications can execute on this chip exactly as they would on a traditional chip. Because this chip is constructed from discrete dies, the difference between local communication within a functional core and between functional cores is more pronounced. Thus, it is especially critical for performance on such a chip that an application be carefully partitioned and mapped to the functional cores.

Figure 1.1: Cross-section of brick and mortar chip.

## 1.2.2 Key advantages

Before delving into the details of brick and mortar chip design, we highlight, qualitatively, the central reasons we pursue this research. The remainder of this thesis will revisit these issues with quantitative analysis.

- Reduced cost. This is the chief motivation for brick and mortar chips. The aim is to produce a low-cost alternative to ASIC chips. The cost savings of brick and mortar stems from mass-production of the constituent parts. Although the components themselves are ASICs, they are produced in bulk to be reused in a variety of end user designs. This reuse amortizes the design and verification cost of the components across multiple products. In addition, bricks are small, resulting in lower individual design and verification costs to begin with.

- Compatible design flow. Today ASIC designers employ significant amounts of existing IP to produce chips. This improves design reliability and saves design time. In such design flows, the IP blocks are provided as "gateware" netlists. The designer integrates these netlists into a complete design which is then manufactured. Brick and mortar is compatible with this design flow, merely moving the bricks from design modules, which fit into synthesis tool flows, to physical bricks, which fit into a manufacturing flow. The IP blocks are pre-manufactured physical entities which will be bonded to a general purpose communication substrate, the I/O cap. In many ways, bricks are the modern-day analogue of the 7400 series of logic, and the I/O cap is the modern wire-wrap board. Rather than spin custom ASICs for products, engineers could purchase these pre-fabricated components and bond them together as needed.

- ASIC-like speed and power. Because most of the logic of a brick and mortar chip exists within a single ASIC component, its performance, in speed and power, will tend to be closer to an ASIC than other custom logic implementation techniques, such as a field programmable gate array (FPGA). When a design calls for it, gate array bricks can implement any necessary custom logic.

- Mixed process integration. As we will show, bricks must comply with a standard

physical and logical interface. They do not, however, have to be built from the same

underlying technology. This makes it readily possible to mix and match bulk CMOS,

SOI, DRAM and other process technologies into the same chip.

- Improved speed. A subtle positive effect with brick and mortar production is that under certain circumstances it can potentially produce higher-performing large chips than an ASIC process. This is because bricks can be partitioned according to speed grade, and chips then produced from parts with like grade.

- Improved yield. Large brick and mortar chips can have a higher yield than large ASICs. The advantage comes from assembling a large chip out of many smaller components. The smaller the component, the higher the yield. One can test component bricks before assembling them, ensuring only functional bricks are included in any assembly, and resulting in an extremely high overall yield.

## 1.2.3 Key challenges

These benefits will not come for free. Brick and mortar chips will achieve them only through careful design of the necessary hardware, software, and manufacturing subsystems:

- Communication network. The communication infrastructure to be implemented in the I/O cap presents a particular challenge. It must be fixed in silicon well before the brick and application layers that are to use it have been determined. Because of this, the communication infrastructure must be general purpose, while also endeavoring to maintain as much of the performance of an application-specific network as possible. This combination, high performance and general, is a very sensitive balance.

- Brick family design. The more applications implementable with brick and mortar the greater the cost savings the system can offer. It is important to keep this need for re-use in mind when designing a brick family. Specifically, the bricks must have appropriate sizes and useful functions.

- Component assembly. Brick and mortar chips introduce a new step to the chip fabrication pipeline: die assembly. It is essential that the assembly technique one uses not be so costly that it erases the savings gained elsewhere by brick and mortar. The assembly options that are available trade off assembly speed and cost.

• Software. Because they reside on different physical dies, there is a greater "distance" between cores in a brick and mortar chip than in a traditional chip. This makes the quality of the application's mapping to computational cores extremely important to overall performance.

#### 1.3 Contributions of the thesis

The contribution of this thesis is the brick and mortar manufacturing system and an analysis of its subsystems.

- An analysis of ASIC manufacturing costs Our model can be used to define the bounds within which brick and mortar can save cost relative to an ASIC.

- A polymorphic on-chip communication network architecture Our on-chip network design space exploration indicates that there is no network that is universally optimal for varying workloads. One can always improve overall performance of a system with varying workloads if the communication network can be tailored to fit each workload. This configurable network can be adapted to the unknown workloads of a brick and mortar chip or to varying workloads on a monolithic chip.

- A brick family design methodology The methodology we present sizes bricks in order to best fit the communication and circuit area needs of the desired IP cores.

- A sample system-on-chip brick family We employ this brick family development methodology to construct a family of bricks for system-on-chip designs.

- Quantification of interaction between component assembly and component

architecture Simulating the assembly of sample chip designs, we discover how the

chip to be assembled affects assembly speed. We propose changes to the assembly

process and component architecture based on these observations.

- A parametrizable software partitioning algorithm An application's mapping onto a highly partitioned chip such as brick and mortar significantly affects its perfor-

mance. We explore existing mapping algorithms and propose a hierarchical, parametrized algorithm which can be tuned to match the application partitioning to the application and to the hardware components.

• A study of brick and mortar CMP implementation We examine a brick and mortar implementation of a chip multiprocessor (CMP) from the perspectives of performance and process variation. We find the SPLASH2 [145] benchmarks execute an average of 36% slower on a brick and mortar chip. This slowdown is disproportionately small relative to the potential cost savings of the brick and mortar technique, and can be removed entirely in some chips by speed binning components prior to assembly.

#### 1.4 Thesis outline

The following chapter presents an economic model of ASIC and brick and mortar chip manufacturing as well as an analysis of the economic opportunity for brick and mortar.

Chapters 3 through 6 examine each of the subsystems required to make brick and mortar a viable ASIC alternative. We work from the bottom of the stack to the top. Accordingly, Chapter 3 starts by presenting a network design for the I/O cap. Next, Chapter 4 examines brick family design and posits a system-on-chip brick family. Chapter 5 examines how to put these components together. In it, we examine manufacturing techniques for assembling and bonding bricks to an I/O cap and for packaging the completed chip. Finally, in Chapter 6 we study algorithms to map software onto tiled chips such as brick and mortar. We analyze existing algorithms and, based on our findings, present a novel, tunable placement algorithm.

In Chapter 7 we look at a brick and mortar case study: a chip multiprocessor design. We examine the performance of a CMP built with brick and mortar, as well as opportunities to exploit process variation amongst the components of this design.

Chapter 8 surveys existing chip manufacturing techniques and how they relate to brick and mortar, as well as technologies related to each of the subsystems examined in Chapters 3 through 6. In the concluding Chapter 9, we discuss potentially attractive variations of the basic brick and mortar proposal presented and explored in this thesis. We also indicate some veins of future research that build on this work.

## Chapter 2

#### MANIPULATING THE ECONOMICS OF CHIP FABRICATION

To quantify the economic benefits of the proposed process we developed a model of chip production costs. This model has two parts. The first part approximates the cost of manufacturing dies in an ASIC process, and the second part calculates the cost of using those dies to produce a brick and mortar chip.

#### 2.1 ASIC cost model

The cost of an ASIC has two components: the non-recurring engineering cost (NRE) that is incurred once for a given design and the unit cost that is incurred once for each chip produced. The top half of Table 2.1 lists the equations that make up this model.

#### 2.1.1 Non-recurring engineering cost

The approximation of ASIC cost is based on several assumptions which are expressed to the model as input parameters. One of the inputs is the assumed NRE. The NRE includes all engineering effort encompassing circuit design, RTL implementation, functional verification, and physical verification of signal integrity, power, and timing. This can take large teams a long time, and with an engineer's time costing upwards of \$380,000 per year [141], the engineering cost is nearly always a seven-figure number. While the engineering cost usually accounts for the largest share of the NRE, the sum includes several other expenses. NREs also encompass the cost of tools, IP licenses if necessary, and photolithographic masks. ASIC design tools typically cost more than \$300,000 [146]. Mask cost has been roughly doubling every technology node, resulting in a complete set of 90nm masks costing between \$1M and \$3M [146].

#### 2.1.2 Unit cost

The unit cost of a chip is the incremental cost of producing each individual chip. In our model we assume a constant unit cost (i.e., the millionth chip costs the same to produce as the first chip), but in reality this is not always the case. Fabs often offer an "economy size" option and discount especially large orders [71]. Also, actual unit costs can shrink, as fabs refine their processes and become more efficient over time.

**Fabrication:** Our approximation of unit cost starts by looking up published processed wafer costs from IC Knowledge [60]. We calculate how many whole dies of a given size fit on a wafer. Dividing the cost of a processed wafer by this number produces the cost of each die.

Test: In 2000, the cost to test each transistor was 10% of the cost to manufacture it. However, as transistors become cheaper and testing becomes more difficult, it is projected that by 2015 it will cost more to test a transistor than to make it [73]. To approximate the cost of testing the dies, we first approximate die test time by assuming a base, constant test time for maneuvering the die to and from the test harness. We then add to it some additional test time proportional to the die area. We compute the die test cost from this test time using an assumed test cost per hour. The manufacturing yield is the percentage of manufactured devices which pass post-manufacturer testing. Every die that fails testing still incurred the manufacturing and test expenses, driving up the effective cost of each working die. We estimate the yield based on an assumed defect rate per unit area and then apply it to the total die cost.

Given these two components, NRE, and UnitCost, the total cost of producing a batch of x chips is simply  $NRE + x \cdot UnitCost$ . This makes the price of one of those x chips  $\frac{NRE + x \cdot UnitCost}{x}.$

## 2.2 Opportunity for brick and mortar

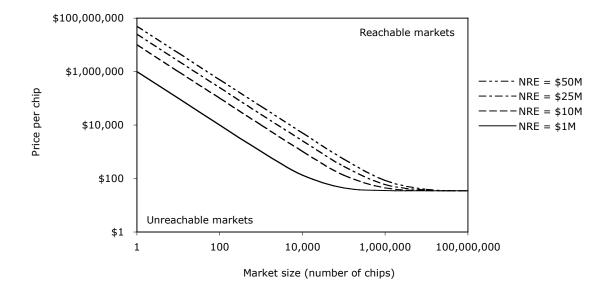

Using this model we can analyze the open window of opportunity for brick and mortar. In Figure 2.1 we have plotted the price of a chip (in the y dimension) produced at a given volume (in the x dimension). Note that this is a log-log plot. Each line indicates the chip

Table 2.1: ASIC and brick and mortar chip cost models.

| ASIC cost             |   |                                                                                   |  |  |  |

|-----------------------|---|-----------------------------------------------------------------------------------|--|--|--|

|                       |   | Inputs                                                                            |  |  |  |

| Wafer Diameter        |   | 200mm and 300mm wafers in production today                                        |  |  |  |

| Feature Size          |   | This is the technology node: 130nm, 90nm, etc.                                    |  |  |  |

| MaskLayers            |   | Data available from IC Knowledge [60] for 24 and 26 layer processes               |  |  |  |

| TestCostPerHour       |   | Hundreds of dollars per hour [56]                                                 |  |  |  |

| Fixed Test Time       |   | Assumed no more than a minute                                                     |  |  |  |

| TestTimePerArea       |   | Depends on the process technology, logic, and completeness of test;               |  |  |  |

|                       |   | anywhere from .08 to 2.5 seconds per $mm^2$ [140, 114]                            |  |  |  |

| DefectsPerArea        |   | Can range from 1.0 to 0.1 defects per $cm^2$ [60]                                 |  |  |  |

| NRE                   |   | Varies between \$5M and \$50M [113]                                               |  |  |  |

| Production Volume     |   |                                                                                   |  |  |  |

|                       |   | Equations                                                                         |  |  |  |

| Processed Wafer Cost  | = | $Lookup_{ICKnowledge}(Wafer Diameter, Feature Size, Mask Layers) \\$              |  |  |  |

| WaferArea             | = | $\pi \cdot (\frac{WaferDiameter}{2})^2$                                           |  |  |  |

| Number Dies           | = | $rac{WaferArea}{DieArea} - rac{\pi \cdot WaferDiameter}{\sqrt{DieArea}}$        |  |  |  |

| TestTime              | = | $FixedTestTime + (TestTimePerArea \cdot DieArea)$                                 |  |  |  |

| TestCost              | = | $rac{TestCostPerHour}{60\ cdot60} \cdot TestTime$                                |  |  |  |

| Die Yield             | = | $(\frac{1+DefectsPerArea\cdot DieArea}{\alpha})^{-\alpha}$                        |  |  |  |

| UnitCost              | = | $rac{WaferCost}{NumberDies} + TestCost}{DieYield}$                               |  |  |  |

| ASICCost              | = | $\frac{NRE+ProductionVolume \cdot UnitCost}{ProductionVolume}$                    |  |  |  |

| Brick and mortar cost |   |                                                                                   |  |  |  |

|                       |   | Inputs                                                                            |  |  |  |

| IOCapCost             |   | From ASIC cost model                                                              |  |  |  |

| NumBricks             |   | Can be anything, but we expect numbers in the 32 to 64 range                      |  |  |  |

| Assembly Cost         |   | Low, simply the cost of the liquid and polymer for the shaker table               |  |  |  |

| TestTime              |   | Assumed the same as ASIC                                                          |  |  |  |

| TestCostPerHour       |   | Assumed the same as ASIC                                                          |  |  |  |

| Yield                 |   |                                                                                   |  |  |  |

|                       |   | Equations                                                                         |  |  |  |

| TestCost              | = | $\frac{TestCostPerHour}{60\cdot60} \cdot TestTime$                                |  |  |  |

| Yielded Chip Cost     | = | $\frac{(IOCapCost + NumBricks \cdot BrickCost) + AssemblyCost + TestCost}{Yield}$ |  |  |  |

price assuming a different NRE ranging from \$1M to \$50M.<sup>1</sup> As one can see from the y-intercepts, if only a single chip is produced, the effective price of that chip is dominated by the NRE. However, as more and more chips are produced, the NRE is amortized away and the price of a chip asymptotically approaches the unit price.

Figure 2.1: Effect of increased non-recurring engineering costs on chip production cost at different market sizes and price points.

There are multiple ways to analyze this data. The first is to track the price of a particular chip as NREs grow. For example, in order to maintain a price of \$100 per chip as the NRE grows from \$1M to \$50M, a market must increase in size from 15,298 to 764,877 units. Alternately, if one maintains a fixed market size of 1M units, the price of a chip will more than double from \$35.63 to \$84.63.

A second analysis takes the plot as a two dimensional market space that is split into two regions by the lines. In this view, one can plot any chip market, real or hypothetical, in the space using the size of the market (x-value) and the chip price it will support (y-value).

<sup>&</sup>lt;sup>1</sup>The other ASIC cost model inputs that generated this plot are: WaferDiameter = 300mm, FeatureSize = 90nm, MaskLayers = 26, TestCostPerHour = \$500, FixedTestTime = 1 minute, TestTimePerArea = 1 second, DefectsPerArea = 0.5 defects per  $cm^2$ .

Any markets that fall upwards of a given line are considered reachable. This means that one can produce chips and sell them to this market at a profit (however small). On the other hand, if a market falls below a line, it is considered unreachable, meaning that the market cannot support the cost of chip production. This plot illustrates the phenomenon alluded to in Chapter 1, that increasing NREs make small, low-cost markets unreachable. As NREs increase, the line separating reachable and unreachable markets creeps upward and to the right, away from inexpensive, low-volume markets. These are the markets that brick and mortar aims to serve.

#### 2.3 Brick and mortar cost model

We estimate the cost of a brick and mortar chip by building on the ASIC cost model from Section 2.1. We use this model to compute the cost of the bricks and I/O cap. To the cost of the components, we add the cost of assembling them and testing the assembled chip. The yield then can be applied to this raw cost to produce an estimate of the yielded brick and mortar chip cost.

## 2.4 Quantifying the advantage of brick and mortar

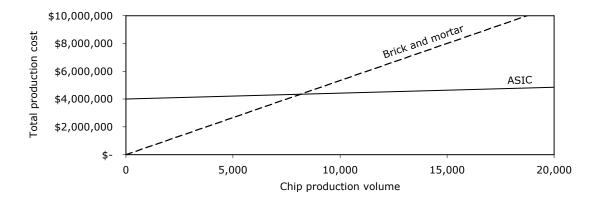

Figure 2.2: Comparison of total production cost for ASIC and brick and mortar chips as a function of batch size.

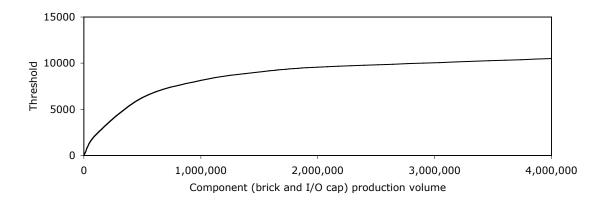

Figure 2.3: Brick and mortar threshold batch size as a function of brick and I/O cap production volume.

The purpose of brick and mortar is to provide a more economical option than ASICs for small batches of chips. Figure 2.2 plots the total production cost of a batch of chips as a function of the size of the batch for both ASIC and brick and mortar.<sup>2</sup> The NRE of each technology determines the y-intercept of these lines (the expense incurred before a single chip is produced) while the unit cost determines the slope (the cost to churn out each individual chip). We call the production volume at which these two lines cross the "threshold". If one's desired batch of chips exceeds the threshold, it is more cost-effective to build an ASIC. However, if one's batch is smaller than the threshold, brick and mortar will be more economical.

The value of this threshold indicates the utility of brick and mortar. The larger the threshold, the more markets brick and mortar can serve cost-effectively. Figure 2.3 plots the threshold as a function of the assumed component production volume (i.e., brick and I/O cap production volume). Note the positive correlation between these two values. The larger the batches of components, the less expensive they will be.<sup>3</sup> Less expensive components

<sup>&</sup>lt;sup>2</sup>The ASIC model inputs for the brick and I/O cap were the same as Figure 2.1 including NRE = \$4M and ProductionVolume = 1,000,000. The brick and mortar model assumes 32 bricks per chip.

<sup>&</sup>lt;sup>3</sup>As Figure 2.1 illustrates, the price reduction is asymptotic towards the unit price of a chip.

means less expensive brick and mortar chips, which will push the threshold volume for building an ASIC even higher.

In our analysis, the component production volume is the independent variable (x), but in practice its value will depend on the threshold (y). The higher the threshold, the more scenarios in which brick and mortar under-prices an ASIC, making it feasible to produce components in larger volumes. In fact, we have a feedback loop in which increasing either variable (threshold or component volume) will increase the other. Thus in designing the brick and mortar process, maximizing either variable will work. Since component production volume is an input to our model, we will seek to maximize the utility of brick and mortar by maximizing the threshold.

## Chapter 3

### POLYMORPHIC ON-CHIP NETWORK

The I/O cap is a silicon die that has three primary functions: (1) to provide power, clock and ground to the bricks; (2) to house I/O pads for connectivity to external package pins; and (3) to provide connectivity between bricks. The first two offer little in the way of brick-and-mortar-specific architectural questions, so we focus on the third to drive the I/O cap design. Because each chip will have the same I/O cap but a unique brick arrangement and application, the interconnect in the I/O cap must be flexible. This chapter examines the communication requirements and proposes a suitably flexible network on-chip (NoC) architecture.

## 3.1 On-chip network design space exploration

To understand the requirements of the I/O cap's network, we conducted an exploration of the NoC design space, examining the performance of different network architectures operating under a range of traffic patterns.

#### 3.1.1 Methodology

**NoC designs.** To explore a wide range of NoC designs, we vary not only the network parameters (e.g., queue capacities and packet sizes) but also the policies and structure of the network itself (e.g., the topology and arbitration algorithm). The first section of Table 3.1 defines the 360 NoCs in our design space.

We selected the topologies to cover a range of radices – from the highly-connected flattened butterfly, to the less-connected ring – and several widely-used topology families. For each topology, we used a deterministic, minimal, oblivious source routing algorithm. The design space includes two buffered arbitration policies: *store-and-forward* and *wormhole* [37] the latter of which reserves and preserves a connection at each switch until all packets in a

message have traversed the switch.

The topology, routing algorithm, and arbitration policy define the network. The performance of a network can vary a great deal based on its resources. Thus we include a range of queue capacities and packet sizes in the design space as well.

**Cycle-level simulation.** We measure the performance of each network using a software micro-architectural network simulator. The simulator is execution-driven and models the network on a cycle-by-cycle basis. We validated this simulator by successfully reproducing data from prior work [139].

Traffic patterns. The cores interact with the network using arbitrary-length messages which are converted to and from fixed-length packets by converters at the boundaries of the network. To drive the simulations, we use three synthetic workloads. The first of these, uniform random traffic, is a widely used traffic generation pattern, in which each node generates a message every cycle for a randomly chosen recipient node. This workload has traffic characteristics similar to an application with near-random data accesses running on a CMP (e.g., a breadth first graph traversal [152]). For this workload, and the others used in this study, the packets are injected via a Bernoulli process.

The other two workloads are permutation workloads, in which each node sends packets to exactly one other node. This is sometimes called an adversarial pattern, because, unlike in the uniform pattern, the communication load is unbalanced. We experiment with two workloads in this family: random permutation, in which the permutation of sender-to-receiver nodes is randomly generated, and nearest neighbor, in which each sender sends packets to a nearby receiver. The local adversarial pattern reasonably approximates a system-on-chip design in which the designer took care to place communicating blocks near one another to maximally exploit any locality in the application.

**Area model.** As on-chip interconnects are often designed under tight area budgets, it is unrealistic to explore interconnection options on the basis of performance alone. Thus, we adopt the methodology of previous work [14], and develop an area model for a network

design. To balance model accuracy with design space size, we synthesize designs for the base network components, including buffers, queues and crossbars. These base estimates target a 90nm process, using high-performance GT standard cell libraries from Taiwan Semiconductor Manufacturing Company (TSMC) for the memories, and a model of full-custom layout of crossbar interconnects.

Table 3.1 describes the network model in more detail. The inputs to the model are the parameter settings which define a particular network design. The synthesis-based section of the table specifies the base area components, including queue and crossbar areas. We then analytically combine the areas of the base components to estimate the total area of the network circuit. Because networks are wiring-heavy circuits, we conservatively assume a 20% wiring overhead [14] in the cell placement, in addition to the already-accounted-for crossbar.

#### 3.1.2 Results

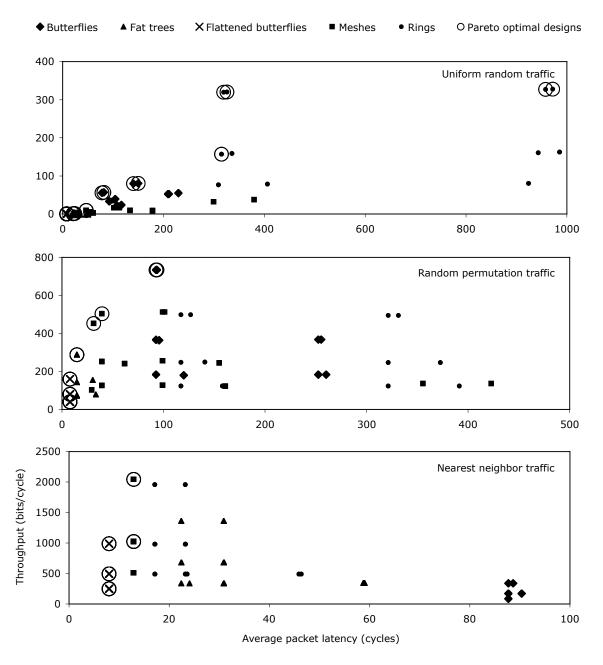

The graphs in Figure 3.1 come from 64-node (N from Table 3.1 = 64) network simulations. On the x-axis is average packet latency while on the y is the average throughput. There is one graph per traffic pattern, with each point in the graphs representing one network design. The circled points indicate the networks that are Pareto optimal for the given workload. These are the designs for which one dimension cannot be improved (latency reduced or throughput increased) without sacrificing in the other dimension (increasing latency or reducing throughput).

First, we examine the design trade-offs when implementing a network for a single traffic pattern. For example, the first graph shows that the Pareto optimal network designs for uniform random traffic include all four topologies. The fat tree and mesh offer the lowest-latency optimal designs, followed by the butterfly with double the latency, and lastly by the ring with quadruple. Over these optimal designs, increases in throughput come only with accompanying increases in latency. With both the fat tree and mesh, short queues (4 entries) and large packets (128 bits) give rise to the aggregate optimal performance. At the other end of the spectrum, the ring, when provisioned with the same large packets, has a

Table 3.1: On-chip network design space and hybrid synthesis-analytical area model

|                                                                          | Description                      | Symbol         | Range                                                                                                                                                                                      |  |

|--------------------------------------------------------------------------|----------------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                          | Number Of Terminals              | N              | 16,64,256,1024                                                                                                                                                                             |  |

|                                                                          |                                  |                | $\int butterfly (k=2)$                                                                                                                                                                     |  |

|                                                                          |                                  |                | $\begin{cases} fat \ tree \ (k = 2, levels = 3) \\ flattened \ butterfly \ (k = 2) \end{cases}$                                                                                            |  |

| Topology                                                                 |                                  | T              | $\begin{cases} flattened butter flu & (k = 2) \end{cases}$                                                                                                                                 |  |

|                                                                          |                                  |                | mesh                                                                                                                                                                                       |  |

|                                                                          |                                  |                |                                                                                                                                                                                            |  |

|                                                                          | B 41                             | -              | ( ring                                                                                                                                                                                     |  |

| Routing Algorithm                                                        |                                  | R              | deterministic                                                                                                                                                                              |  |

| Arbitration Algorithm                                                    |                                  | A $M$          | store-and-forward, wormhole 256                                                                                                                                                            |  |

|                                                                          | Message Size<br>Packet Size      |                | 32, 64, 128                                                                                                                                                                                |  |

| Facket Size Switch Packet Queue Capacity Converter Packet Queue Capacity |                                  | P $SQ$         | 4, 16, 64                                                                                                                                                                                  |  |

|                                                                          |                                  | CPQ            | 4, 16, 64                                                                                                                                                                                  |  |

|                                                                          | Converter Message Queue Capacity | CMQ            | 4                                                                                                                                                                                          |  |

| Synthesis-A                                                              | Analytical Area Model            |                |                                                                                                                                                                                            |  |

|                                                                          | Description                      | Symbol         | Value                                                                                                                                                                                      |  |

|                                                                          | Queue area                       | $Queue_{area}$ | $0.00002 \ mm^2/bit$                                                                                                                                                                       |  |

| Synthesis                                                                | Wire pitch                       | x              | 0.00024mm [63]                                                                                                                                                                             |  |

|                                                                          | Crossbar area                    | $XBar_{area}$  | $\chi^2 \times D_{in} \times D_{out} \times P^2$ [39]                                                                                                                                      |  |

|                                                                          | Wire overhead                    | $W_{area}$     | 20%                                                                                                                                                                                        |  |

| Analytical                                                               |                                  |                | $\frac{N}{k} \times log(N)$ if T is butterfly                                                                                                                                              |  |

|                                                                          |                                  |                | $ \begin{cases} \frac{N}{k} \times log(N) & \text{if } T \text{ is } butterfly \\ \frac{N}{k} & \text{if } T \text{ is } flattened \ butterfly \end{cases} $                               |  |

|                                                                          | Number Of Switches               | S              | $\begin{cases} k \\ N + \frac{N}{k^2} + \frac{N}{k^4} & \text{if } T \text{ is } fat  tree \end{cases}$                                                                                    |  |

|                                                                          |                                  | ~              |                                                                                                                                                                                            |  |

|                                                                          |                                  |                | N if $T$ is $mesh$                                                                                                                                                                         |  |

|                                                                          |                                  |                | N if $T$ is $ring$                                                                                                                                                                         |  |

|                                                                          |                                  |                | $k + log_k(\frac{N}{k})$ if T is flattened butterfly                                                                                                                                       |  |

|                                                                          |                                  |                | k if T is butterfly                                                                                                                                                                        |  |

|                                                                          |                                  |                | $\int_{0}^{\infty} 2 if leaf$                                                                                                                                                              |  |

|                                                                          | Switch Degree                    | D              | $\begin{cases} 2 & \text{if leaf} \\ k^2 + 1 & \text{if internal} & \text{if } T \text{ is } fat \text{ tree} \\ k^2 + 4 & \text{if root} \end{cases}$ $5 & \text{if } T \text{ is } mesh$ |  |

|                                                                          |                                  |                | $k^2 + 4$ if root                                                                                                                                                                          |  |

|                                                                          |                                  |                | (" + 1 t) 100t                                                                                                                                                                             |  |

|                                                                          |                                  |                | I                                                                                                                                                                                          |  |

|                                                                          |                                  |                | 3 if $T$ is $ring$                                                                                                                                                                         |  |

|                                                                          | Switch Queue Area                | $SQ_{area}$    | $SQ \times P \times Queue_{area}$                                                                                                                                                          |  |

|                                                                          | Switch Area                      | $S_{area}$     | $SQ_{area} \times D + XBar_{area} + SQ_{area} \times D$                                                                                                                                    |  |

|                                                                          |                                  | $CMQ_{area}$   | $CMQ \times QPB$                                                                                                                                                                           |  |

|                                                                          | Converter Message Queue Area     |                |                                                                                                                                                                                            |  |

|                                                                          | Converter Packet Queue Area      | $CPQ_{area}$   | $CPQ \times QPB$                                                                                                                                                                           |  |

|                                                                          |                                  |                |                                                                                                                                                                                            |  |

Figure 3.1: Latency and throughput of on-chip interconnect design space.

long transmission latency, but offers significantly higher throughput.

In the case of random adversarial traffic, Figure 3.1 indicates that a fat tree once again offers the lowest-latency communication option. As with uniform random communication, some communicating nodes are going to be at a distance in the network, and thus, the non-neighbor connections proffered by the higher levels of the tree speed that traversal. The differences in throughput amongst the fat tree designs on this workload are entirely attributable to packet size: the larger the packet the higher the throughput. This is feasible under the area budget, because the network does not require particularly deep queues on this workload. The same is true of the mesh network, for which the best designs incorporate large packets (128 bits) and short queues (4 entries) to maximize throughput under the area budget. However, on average, the packet latency through the mesh is slightly higher than the fat tree due to the neighbor-only links.

By contrast, the local adversarial traffic experiences exactly the opposite result. While random traffic latency *suffered* on neighbor-only topologies, the local adversarial traffic, which *is* neighbor-only, took good advantage of those topologies. Thus, for this workload, the mesh topologies are optimal, with the ring not far behind.

While we see that there is a network to fit each workload, there is no network to fit all workloads. In other words, no network in the design space is optimal across all three workloads. The optimal designs often differ in topology, and, when the topologies are the same, the resource provisioning is very different. Although these workloads are synthetic, it would not be far-fetched to encounter three similar patterns in the I/O cap, depending on the brick selection and the application or input data set that is running. Unfortunately, in selecting a single network, one will necessarily have to sacrifice performance on one or more workloads.

### 3.2 Polymorphic network microarchitecture

Having empirically realized that no single fixed-design on-chip network efficiently communicates different styles of traffic, we have designed the polymorphic on-chip network. This network can be configured at runtime to mimic traditional fixed-function networks. From a hardware standpoint, the network is built from a sea of resources, namely buffers and cross-

bars. Careful design allows post-fabrication or even runtime configuration of these resources to form an interconnect with a custom topology, buffer allocation, and packet size.

Such a network should be useful in a brick and mortar I/O cap where the brick configuration and application are unknown at the time the cap is fabricated. The polymorphic network would also be useful in a more standard monolithic device that will run multiple applications. The data, presented in Section 3.1.2, indicate that, even with a fixed hardware configuration, varying applications alone are sufficient to produce network workloads which benefit significantly from a customized network. The discussion of the polymorphic network will continue with the I/O cap use in mind, but will comment on this potential alternate use when appropriate. First we will describe the microarchitecture of the configurable fabric, followed by some examples of how to take advantage of the polymorphism.

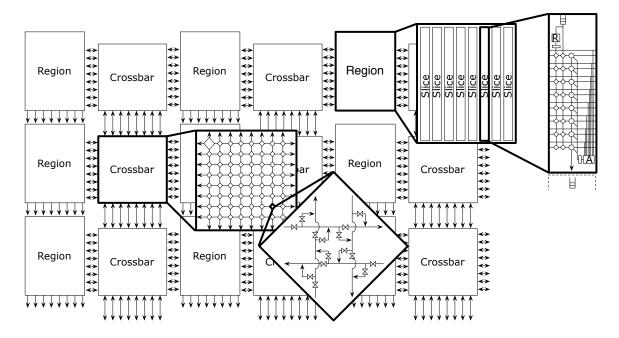

# 3.2.1 Configurable switches

A switch in the polymorphic network, like a classic switch, consists of input and output packet queues, routers, arbiters and a crossbar of connections. As illustrated in Figure 3.2, we call the set of input queue, router, and arbiter a *slice*. These slices are clustered into *regions*. Although Figure 3.2 illustrates eight slices per region, in the following section we will explore different parametrizations of this underlying fabric structure.

The crossbar connecting the slices in a region is a double crossbar that allows redefinition of the input connections as well as the usual dynamic definition of output connections. The diamond-shaped intersections on the incoming packet lines in Figure 3.2's slice detail denote the static connections, while the circular intersections indicate the dynamically switching output connections. Although Figure 3.2 shows these crossbars as bidirectional, they in fact consist of two unidirectional wires, because drive buffers can be employed only on directed wires. This makes these wires physically segmentable, with a potential segmentation point between each of the slices.

Each slice supports two virtual channels, which can share the available buffer space, using a flexible sharing scheme [38]. Networks requiring more than two channels, must aggregate multiple slices together.

Figure 3.2: Microarchitecture of the polymorphic on-chip network.

The configurable connections between input wires and crossbars and the ability to segment a crossbar make it possible to construct switches out of slices from different regions in the fabric. This ability to aggregate slices from different regions into one logical switch turns out to be very valuable, as it permits a dense packing of switches in the fabric. This has two benefits. First, as the input and output queues consume most of the area of this fabric, it is important to waste as few of them as possible when configuring the network. Second, the closer the switches are physically, the shorter the routed links that connect them must be, leading to less link routing congestion and less capacitive load on those links.

Imagine if one had an 8-slice region configured as two  $4 \times 4$  switches consuming all of the eight crossbars in the region. The ability to segment a crossbar allows us to make one of those switches larger if we desire, increasing it to a  $5 \times 5$ , by pulling in a slice from a neighboring region. This new slice must connect its input to a crossbar that is not already used within its own switch, meaning it must connect to a crossbar that the other switch is using, which is possible only if the wires of the crossbar can be physically disconnected.

## 3.2.2 Packet routing and arbitration

Each network slice contains routing and arbitration logic. These two pieces of logic serve the same function as the router and arbiter in their classic switch counterparts. A router is associated with an input queue and determines to which output to route the first packet in the queue. Meanwhile each output queue has an associated arbiter which arbitrates write access to the output queue amongst the requesting inputs.

The polymorphic network uses source routing, where each packet carries its pre-computed route with it, rather than making routing decision at each point in the network. This allows the network to support any static routing scheme, such as the one used in the design space exploration presented in Section 3.1. However, this adds bits to the packet header, reducing the payload of a fixed-size packet. One way to work around this, which we employ, is to implement wormhole arbitration [36], allowing a lead packet to carry the route and establish necessary connections, that are used by the subsequent packets belonging to the same message.

Configurable link resources. The crossbars and any wires unemployed in switches can implement connections between the switches. These connections are statically routed by an FPGA-like wire routing algorithm. The connections in these crossbars are statically configurable. They will implement one fixed topology per configuration.

Interface to cores. The polymorphic fabric will be connected to cores in much the same way as a normal network-on-chip. One common network technique is to *concentrate* network traffic, essentially gathering traffic from multiple cores and injecting it into one network node. In a classic network, this resource sharing technique reduces the total size of the network. If concentration or a similar technique would effect the workload in such a way as to improve performance, the polymorphic fabric can readily be configured to concentrate traffic upon injection into the network.

Configuration mechanism. Like an FPGA, the polymorphic fabric is configured via bitstream. This bitstream can originate either from an on-chip memory or from an external

source. In the first case, the OS or runtime system can configure the network by writing to memory-mapped bits containing the configuration as it would any other I/O device. This configuration technique would also work on a non-brick and mortar chip. The device could also include a default network configuration to support applications which do not specify their own custom interconnect. The question of when and how to reconfigure the polymorphic fabric in such a chip is an open and future question that is elaborated on at the end of this thesis in Section 9.2.

# 3.3 Example configurations

The fabric microarchitecture we have described makes it possible to customize the implemented networks. The customization can happen in several ways including custom topology, custom buffering, and custom packet size.

### 3.3.1 Custom topologies

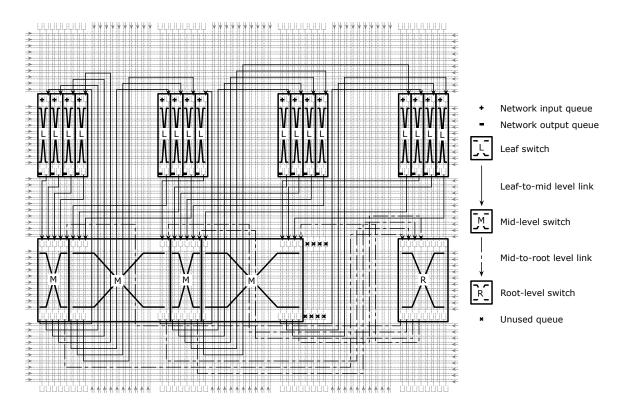

Configuration of the fabric to implement a particular topology is a matter of forming appropriately-sized switches and connecting them according to the desired topology. Figure 3.3 illustrates the mapping of a segment of a fat tree onto the fabric. It is a four-way fat tree with three levels (the same topology used in the design space exploration in Section 3.1.1). For legibility, we show the sub-tree of only one root node. In a full tree, the unused routing resources on the north, south and east edges of this diagram are used to connect multiple nodes together. Note that in the regions occupied by this design, only 8 of the 128 queues are not part of a switch and have gone unused. They are indicated by "x" in Figure 3.3. The ability to form switches out of slices in adjacent regions enables this high queue utilization. We have demonstrated the instantiation of a fat tree, because, with highly-connected, high-degree switches, it demands a careful configuration of the fabric.

## 3.3.2 Custom buffer allocation

One can use this fabric to increase the size of the logical buffers in the switches. By configuring a single slice to connect the input queue directly to the output queue, one forms

Figure 3.3: Instantiation of a fat tree network in polymorphic fabric. The links that form the mesh connections between root nodes are not shown.

a single logical buffer from two physically separate ones. In this buffer, packets advance from the back half of the buffer to the front half automatically, as necessary. Another way to view such a configuration is as a  $1 \times 1$  switch, which does not route or switch, but simply advances packets forward as a queue would.

Switch buffer resources can be increased individually. One can selectively increase buffers on certain switches or ports as the application may demand. This capability dovetails nicely with other research that develops tools to identify the ideal network configuration, including buffer allocation, for an application [64, 90, 57].

# 3.3.3 Custom packet size

Finally, one can also increase the network packet size. Instead of aggregating sequential buffers, as in the previous example, one aggregates parallel buffers and links. In effect, this increases the network's packet size by increasing the datapath width. Both of these queue enlargement techniques increase the per-switch, or per-link resource usage requirements of the fabric. However, with the polymorphic fabric, the increased resource usage is commensurate with the analogous increase in resources of a classic ASIC interconnect.

Note that the polymorphic network configuration need not be restricted solely to generalpurpose interconnects. It can support nearly arbitrary application-by-application tailoring. The performance benefits of such customization are well-documented in the literature [57, 53, 90], but were previously unattainable on a single hardware design.

## 3.4 Polymorphic fabric parametrization

The microarchitecture presented in the previous section outlines a schema of a polymorphic fabric for implementing on-chip networks. Several parameters remains unspecified. These parameters must be defined in order to actually implement a polymorphic fabric and are listed in the first section of Table 3.2.

### 3.4.1 Parameter space

As Table 3.2 states, there are N slices to a region, each containing a queue that is W bits wide and D entries deep. Each region has two  $N \times H$  crossbars where H (the number of horizontal bars) must be at least N (the number of slices in each region). Similarly, each crossbar outside the regions is a  $V \times H$  crossbar. We explore the parameter space of polymorphic fabrics defined in the first section of Table 3.2, totaling 108 polymorphic fabrics in all.

Based on the parameters, we can calculate the area of the *base element* of the fabric. The base element consists of a region and a crossbar and is the minimal unit of fabric. Multiple base elements can be produced to form larger swaths of fabric. The second section of Table 3.2 details how the area of a base element is computed. In a region, there are N

Table 3.2: Polymorphic fabric design space and area and configuration models.

|                    | Description                                  | Symbol                         | Range                                                                                                        |  |  |

|--------------------|----------------------------------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------|--|--|

|                    | Number of slices per region                  | N                              | 2,4,8,16                                                                                                     |  |  |

|                    | Queue width                                  | W                              | 32,64,128                                                                                                    |  |  |

|                    | Queue depth                                  | D                              | 4,16,64                                                                                                      |  |  |

|                    | Width of horizontal configurable link tracks | H                              | N,~2 	imes N                                                                                                 |  |  |

|                    | Width of vertical configurable link tracks   | V                              | N,2 	imes N                                                                                                  |  |  |

|                    | Network configuration                        | C                              | each network in first section of Table 3.1                                                                   |  |  |